원문 버전 : 2022년 AN2586 Rev 8

번역 및 수정 편집 : 공학박사 이철호(zullio@naver.com)

최종 수정 : 2023년 4월 25일

소개

이 문서는 전원 공급 장치, 클록 관리, 재설정 제어, 부팅 모드 설정 및 디버그 관리와 같은 개발 보드 기능의 하드웨어 구현 개요가 필요한 시스템 설계자를 대상으로 한다.

이 문서에서는 저밀도 밸류 라인, 저밀도, 중밀도 밸류 라인, 중밀도, 고밀도, XL 밀도 및 연결성 라인 STM32F10xxx 제품(전체 목록은 표 1에 자세히 설명되어 있음)을 사용하는 방법을 보여준다. 그리고 응용 프로그램을 개발하는 데 필요한 최소 하드웨어 리소스를 설명한다.

주요 구성 요소, 인터페이스 및 모드에 대한 설명과 함께, 자세한 참조 디자인 도식도 제공된다.

표 1. 적용 제품

| 유형 | 라인 |

| 마이크로컨트롤러 | STM32F100 밸류 라인 STM32F101 STM32F102 STM32F103 STM32F105/107 |

차례

| 1 | 일반 정보 ------------------------------------------------------------------------ | 6 | ||

| 2 | 전원 공급 장치 ------------------------------------------------------------------- | 7 | ||

| 2.1 | 소개 ----------------------------------------------------------------------- | 7 | ||

| 2.1.1 2.1.2 2.1.3 |

독립적인 A/D 컨버터 공급 및 기준 전압 ------------------------------- 배터리 백업 --------------------------------------------------------- 전압 레귤레이터 --------------------------------------------------------- |

7 8 8 |

||

| 2.2 | 전원 공급 방식 ------------------------------------------------------------- | 8 | ||

| 2.3 | 리셋 및 전원 공급 장치 감독자 ---------------------------------------------- | 9 | ||

| 2.3.1 2.3.2 2.3.3 |

파워 온 리셋(POR) / 파워 다운 리셋(PDR) ----------------------------- 프로그래밍 가능한 전압 검출기(PVD) ---------------------------------- 시스템 재설정 ------------------------------------------------------- |

9 10 10 |

||

| 3 | 클록 ----------------------------------------------------------------------------- | 12 | ||

| 3.1 | HSE OSC 클록 --------------------------------------------------------------- | 12 | ||

| 3.1.1 3.1.2 |

외부 소스(HSE 바이패스) --------------------------------------------- 외부 수정/세라믹 공진기(HSE 수정) ----------------------------------- |

13 13 |

||

| 3.2 | LSE OSC 클록 --------------------------------------------------------------- | 12 | ||

| 3.2.1 3.2.2 |

외부 소스(LSE 바이패스) --------------------------------------------- 외부 수정/세라믹 공진기(LSE 수정) ----------------------------------- |

14 14 |

||

| 3.3 | 시계 보안 시스템(CSS) ------------------------------------------------------ | 15 | ||

| 4 | 부팅 구성 ------------------------------------------------------------------------ | 16 | ||

| 4.1 4.2 4.3 |

부팅 모드 선택 ------------------------------------------------------------- 부트 핀 연결 --------------------------------------------------------------- 임베디드 부트로더 모드 ----------------------------------------------------- |

16 16 17 |

||

| 5 | 디버그 관리 ---------------------------------------------------------------------- | 18 | ||

| 5.1 5.2 5.3 |

소개 ----------------------------------------------------------------------- SWJ 디버그 포트(직렬 와이어 및 JTAG) --------------------------------------- 핀아웃 및 디버그 포트 핀 --------------------------------------------------- |

18 18 18 |

||

| 5.3.1 5.3.2 5.3.3 5.3.4 |

SWJ 디버그 포트 핀 -------------------------------------------------- 유연한 SWJ-DP 핀 할당 ----------------------------------------------- JTAG 핀의 내부 풀업 및 풀다운 저항 ---------------------------------- 표준 JTAG 커넥터와 SWJ 디버그 포트 연결 ----------------------------- |

18 19 20 20 |

||

| 6 | 권장 사항 ----------------------------------------------------------------------- | 21 | ||

| 6.1 6.2 6.3 6.4 6.5 6.6 |

인쇄 회로 기판 ------------------------------------------------------------- 구성 요소 위치 ------------------------------------------------------------- 접지 및 전원 공급(VSS, VDD) ------------------------------------------------ 디커플링 ------------------------------------------------------------------- 기타 신호 ------------------------------------------------------------------ 사용하지 않는 I/O 및 기능 -------------------------------------------------- |

21 21 21 21 22 22 |

||

| 7 | 참조 디자인 ---------------------------------------------------------------- | 23 | ||

| 7.1 | 설명 ----------------------------------------------------------------------- | 23 | ||

| 7.1.1 7.1.2 7.1.3 7.1.4 7.1.5 |

클록 ---------------------------------------------------------------- 재설정 -------------------------------------------------------------- 부트 모드 ----------------------------------------------------------- SWJ 인터페이스 ------------------------------------------------------ 전원 공급 ----------------------------------------------------------- |

23 23 23 23 23 |

||

| 7.2 | 컴포넌트 참조 -------------------------------------------------------------- | 24 | ||

| 8 | 개정 내역 ------------------------------------------------------------------------ | 28 | ||

역자 주 : 페이지 번호는 원문 기준이므로 이 문서에서는 차이가 날 수 있음.

테이블 목록

| 표 1. 표 2. 표 3. 표 4. 표 5. 표 6. 표 7. 표 8. |

적용 가능한 제품 ----------------------------------------------------------- 부팅 모드 ------------------------------------------------------------------ 디버그 포트 핀 할당 -------------------------------------------------------- SWJ I/O 핀 가용성 ---------------------------------------------------------- 필수 구성 요소 ------------------------------------------------------------- 선택적 구성 요소 ----------------------------------------------------------- 모든 패키지에 대한 참조 연결 ----------------------------------------------- 문서 개정 내역 ------------------------------------------------------------- |

1 16 19 19 24 24 26 28 |

그림 목록

| 그림 1. 그림 2. 그림 3. 그림 4. 그림 5. 그림 6. 그림 7. 그림 8. 그림 9. 그림 10. 그림 11. 그림 12. 그림 13. 그림 14. |

전원 공급 장치 개요 ------------------------------------------------------- 전원 공급 방식 ------------------------------------------------------------ 파워 온 리셋/파워 다운 리셋 파형 ------------------------------------------ PVD 임계값 ---------------------------------------------------------------- 리셋 회로의 단순화된 다이어그램 ------------------------------------------- 외부 클럭 ----------------------------------------------------------------- 수정/세라믹 공진기 -------------------------------------------------------- 외부 클럭 ----------------------------------------------------------------- 수정/세라믹 공진기 -------------------------------------------------------- 부팅 모드 선택 구현 예 ---------------------------------------------------- 호스트-보드 연결 ---------------------------------------------------------- JTAG 커넥터 구현 ---------------------------------------------------------- VDD/VSS 쌍의 일반적인 레이아웃 -------------------------------------------- STM32F103ZE(T6) 마이크로컨트롤러 참조 회로도 ------------------------------ |

7 9 9 10 11 12 12 14 14 16 18 20 22 25 |

1 일반 정보

이 문서는 Arm® Cortex® 코어를 기반으로 하는 STM32F10xxx 마이크로컨트롤러에 적용된다.

참고: Arm은 미국 및/또는 기타 국가에서 Arm Limited(또는 자회사)의 등록 상표된다.

용어 사전

- 저밀도 밸류 라인 장치는 STM32F100xx 마이크로컨트롤러로, 플래시 메모리 밀도 범위는 16~32KB이다.

- 저밀도 장치는 STM32F101xx, STM32F102xx 및 STM32F103xx 마이크로컨트롤러이며 플래시 메모리 밀도 범위는 16~32KB이다.

- 중밀도 밸류 라인 장치는 플래시 메모리 밀도가 64~128KB인 STM32F100xx 마이크로컨트롤러이다.

- 중간 밀도 장치는 STM32F100xx, STM32F101xx, STM32F102xx 및 STM32F103xx 마이크로컨트롤러이며, 플래시 메모리 밀도 범위는 64~128KB이다.

- 고밀도 밸류 라인 장치는 STM32F100xx 마이크로컨트롤러로, 플래시 메모리 밀도 범위는 256~512KB이다.

- 고밀도 장치는 STM32F101xx 및 STM32F103xx 마이크로컨트롤러이며, 플래시 메모리 밀도 범위는 256~512KB이다.

- XL 밀도 장치는 STM32F101xx 및 STM32F103xx 마이크로컨트롤러이며 플래시 메모리 밀도 범위는 768KB에서 1MB 사이이다.

연결 라인 장치는 STM32F105xx 및 STM32F107xx 마이크로컨트롤러이다.

2 전원 공급 장치

2.1 소개

이 장치에는 2.0 ~ 3.6V 작동 전압 공급(VDD)이 필요하다.

내장된 레귤레이터는 내부 1.8V 디지털 전원을 공급하는 데 사용된다.

RTC(실시간 클록) 및 백업 레지스터는 주 VDD 공급 장치의 전원이 꺼지면, VBAT 전압에서 전원을 공급받을 수 있다.

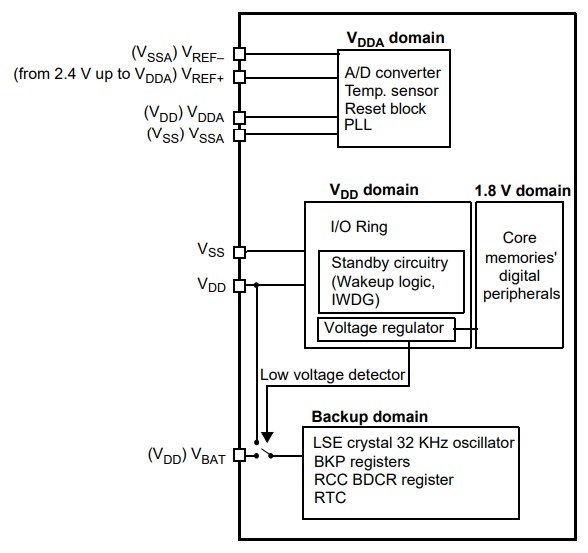

그림 1. 전원 공급 장치 개요

참고: VDDA 및 VSSA는 각각 VDD 및 VSS에 연결되어야 한다.

2.1.1 독립적인 A/D 컨버터 공급 및 기준 전압

변환 정확도를 개선하기 위해 ADC에는 별도로 필터링할 수 있고, PCB의 노이즈로부터 차폐되는 독립 전원 공급 장치가 있다.

• ADC 전압 공급 입력은 별도의 VDDA 핀에서 사용할 수 있다.

• 절연 공급 접지 연결은 VSSA 핀에서 제공된다.

사용할 수 있는 경우(패키지에 따라 다름) VREF–는 VSSA에 연결되어야 한다.

100핀 및 144핀 패키지

저전압 입력에서 더 나은 정확도를 보장하기 위해, 사용자는 VREF+에 별도의 외부 기준 전압 ADC 입력을 연결할 수 있다. VREF+의 전압 범위는 2.4V ~ VDDA이다.

64핀 이하의 패키지

VREF+ 및 VREF- 핀은 사용할 수 없으며, ADC 전압 공급 장치(VDDA) 및 접지(VSSA)에 내부적으로 연결되어 있다.

2.1.2 배터리 백업

VDD가 꺼져 있을 때, 백업 레지스터의 내용을 유지하기 위해, VBAT 핀을 배터리 또는 다른 소스에서 제공하는 선택적 대기 전압에 연결할 수 있다.

VBAT 핀은 또한 RTC 장치에 전원을 공급하므로, 주 디지털 공급 장치(VDD)가 꺼진 경우에도, RTC가 작동할 수 있다. VBAT 전원으로의 스위치는 리셋 블록에 내장된 PDR(Power Down Reset) 회로에 의해 제어된다.

애플리케이션에서 외부 배터리를 사용하지 않는 경우, VBAT를 VDD에 외부적으로 연결하는 것이 좋다.

2.1.3 전압 레귤레이터

리셋 후, 전압 레귤레이터는 항상 활성화된다. 응용 프로그램 모드에 따라 세 가지 모드로 작동한다.

• 실행 모드에서 레귤레이터는 1.8V 도메인(코어, 메모리 및 디지털 주변 장치)에 전체 전력을 공급한다.

• 정지 모드에서 레귤레이터는 1.8V 도메인에 저전력을 공급하여, 레지스터 및 SRAM의 내용을 보존한다.

• 대기 모드에서는 레귤레이터의 전원이 꺼진다. 대기 회로 및 백업 도메인과 관련된 항목을 제외하고, 레지스터 및 SRAM의 내용이 손실된다.

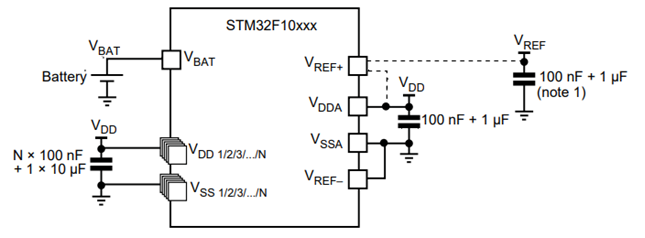

2.2 전원 공급 방식

이 회로는 안정화된 전원 공급 장치인 VDD에 의해 전원이 공급된다.

• VDD 핀은 외부 디커플링 커패시터(VDD 핀당 100nF 세라믹 커패시터 1개와 탄탈룸 또는 세라믹 커패시터 1개(최소 4.7µF, 일반 10µF))를 사용하여, VDD에 연결해야 한다.

• VBAT 핀은 외부 배터리에 연결할 수 있다(1.8V < VBAT < 3.6V). 외부 배터리를 사용하지 않는 경우, 이 핀을 100nF 외부 세라믹 디커플링 커패시터를 사용하여, VDD에 연결하는 것이 좋다.

• VDDA 핀은 2개의 외부 디커플링 커패시터(100nF 세라믹 + 1µF 탄탈륨 또는 세라믹)에 연결해야 한다.

• VREF+ 핀은 VDDA 외부 전원 공급 장치에 연결할 수 있다. 별도의 외부 기준 전압이 VREF+에 적용되는 경우, 100nF 및 1µF 커패시터를 이 핀에 연결해야 한다. 모든 경우에 VREF+는 2.4V와 VDDA 사이에서 유지되어야 한다.

• 아날로그 노이즈를 필터링하기 위해, 추가 예방 조치를 취할 수 있다.

– VDDA는 페라이트 비드를 통해 VDD에 연결할 수 있다.

– VREF+ 핀은 저항(일반 47Ω)을 통해 VDDA에 연결할 수 있다.

주의: ADC를 사용하는 경우, VDD 범위는 2.4 ~ 3.6V로 제한된다(ADC를 사용하지 않는 경우 VDD 범위는 2.0 ~ 3.6V).

그림 2. 전원 공급 방식

1. (선택 사항) 별도의 외부 기준 전압이 VREF+에 연결된 경우, 두 개의 커패시터(100nF 및 1µF)를 연결해야 한다.

2. VREF+는 VDDA 또는 VREF에 연결된다.

3. N은 VDD 및 VSS 입력의 수이다.

2.3 리셋 및 전원 공급 장치 감시자

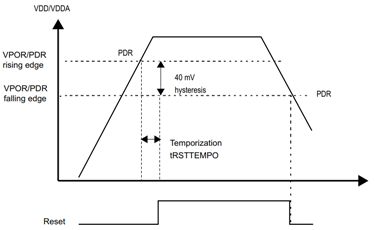

2.3.1 파워 온 리셋(POR) / 파워 다운 리셋(PDR)

이 장치에는 2V에서 시작하여, 적절한 작동을 허용하는 통합 POR/PDR 회로가 있다.

장치는 VDD가 지정된 임계값 VPOR/PDR 미만인 한, 외부 리셋 회로 없이도 리셋 모드를 유지한다. 전원 켜기/전원 끄기 리셋 임계값에 대한 자세한 내용은 저밀도, 중간 밀도, 고밀도, XL 밀도 및 연결 라인 STM32F10xxx 데이터시트의 전기적 특성을 참조하자.

그림 3. 파워 온 리셋/파워 다운 리셋 파형

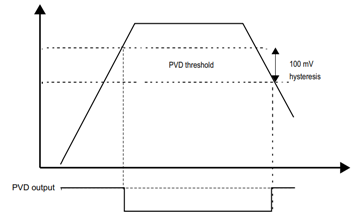

2.3.2 프로그래밍 가능한 전압 검출기(PVD)

PVD를 사용하여 전원 제어 레지스터(PWR_CR)의 PLS[2:0] 비트에서 선택한 임계값과 비교하여, VDD 전원 공급 장치를 모니터링할 수 있다.

PVD는 PVDE 비트를 설정하여 활성화된다.

전력 제어/상태 레지스터(PWR_CSR)에서 PVDO 플래그를 사용하여, VDD가 PVD 임계값보다 높은지 낮은지를 나타낸다. 이 이벤트는 내부적으로 EXTI Line16에 연결되며, EXTI 레지스터를 통해 활성화된 경우, 인터럽트를 생성할 수 있다. EXTI Line16 상승/하강 에지 구성에 따라, VDD가 PVD 임계값 아래로 떨어지거나, VDD가 PVD 임계값 위로 상승할 때, PVD 출력 인터럽트가 생성될 수 있다. 예를 들어 서비스 루틴은 비상 종료 작업을 수행할 수 있다.

그림 4. PVD 임계값

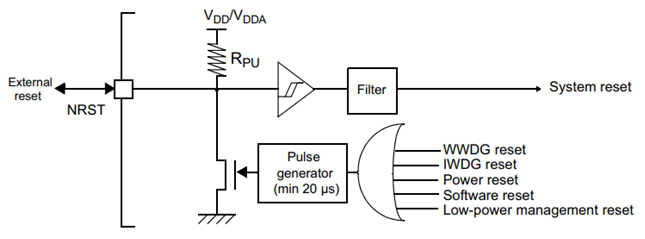

2.3.3 시스템 리셋

시스템 리셋은 클록 컨트롤러 CSR 레지스터의 리셋 플래그와 백업 도메인의 레지스터를 제외한 모든 레지스터를 리셋 값으로 설정한다(그림 1 참조).

다음 이벤트 중 하나가 발생하면, 시스템 리셋이 생성된다.

1. NRST 핀의 로우 레벨(외부 리셋)

2. 윈도우 워치독 카운트 종료 조건(WWDG 리셋)

3. 독립 워치독 카운트 종료 조건(IWDG 리셋)

4. 소프트웨어 리셋(SW 리셋)

5. 저전력 관리 리셋

리셋 소스는 제어/상태 레지스터 RCC_CSR의 재설정 플래그를 확인하여 식별할 수 있다.

STM32F1xx는 올바르게 전원을 켜기 위해, 외부 리셋 회로가 필요하지 않다. 기생 리셋으로부터 장치를 보호하여, EMS 성능을 개선하려면, 풀다운 커패시터만 권장된다. 그림 5를 참조하자.

내부 저항을 통해, 풀다운 커패시터를 충전 및 방전하면, 장치 전력 소비가 증가한다. 커패시터 권장 값(100nF)을 10nF로 줄여, 이 전력 소비를 제한할 수 있다.

그림 5. 리셋 회로의 단순화된 다이어그램

3 클록

세 가지 다른 클록 소스를 사용하여, 시스템 클록(SYSCLK)을 구동할 수 있다.

• HSI 발진기 클록(고속 내부 클록 신호)

• HSE 발진기 클록(고속 외부 클록 신호)

• PLL 클록

장치에는 두 개의 보조 클록 소스가 있다.

• 40kHz 저속 내부 RC(LSI RC), 독립적인 워치독 및 옵션으로 정지/대기 모드에서 자동 웨이크업에 사용되는 RTC를 구동한다.

• 32.768kHz 저속 외부 수정(LSE 수정), 선택적으로 실시간 클록 구동(RTCCLK)

각 클록 소스는 사용하지 않을 때, 독립적으로 켜거나 꺼서, 전력 소비를 최적화할 수 있다.

클록 트리에 대한 설명은 참조 설명서를 참조한다.

• STM32F101xx, STM32F102xx, STM32F103xx 및 STM32F105xx/107xx 마이크로컨트롤러용 RM0008 문서

• STM32F100xx 밸류 라인 마이크로컨트롤러용 RM0041 문서

3.1 HSE OSC 클록

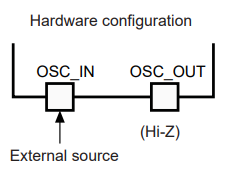

고속 외부 클록 신호(HSE)는 두 개의 클록 소스에서 생성할 수 있다.

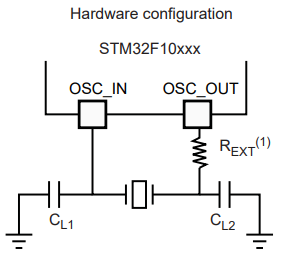

• HSE 외부 수정/세라믹 공진기(그림 7 참조)

• HSE 사용자 외부 클록(그림 6 참조)

그림 6. 외부 클록

그림 7. 수정/세라믹 공진기

1. REXT 값은 크리스탈 특성에 따라 다르다. 일반적인 값은 5 ~ 6 RS(공진기 직렬 저항) 범위이다.

2. 부하 커패시턴스 CL의 공식은 다음과 같다. CL = CL1 x CL2 / (CL1 + CL2) + Cstray, 여기서 Cstray는 핀 커패시턴스와 보드 또는 트레이스 PCB 관련 커패시턴스이다. 일반적으로 2 ~ 7pF이다. 값을 최소화하려면, 섹션 6을 참조하자.

3.1.1 외부 소스(HSE 바이패스)

이 모드에서는 외부 클럭 소스가 제공되어야 한다. 최대 빈도는 다음과 같다.

• STM32F100xx 밸류 라인 장치용 24MHz

• STM32F101xx, STM32F102xx 및 STM32F103xx 장치용 25MHz

• 연결 회선 장치의 경우 50MHz

듀티 사이클이 약 50%인 외부 클록 신호(정사각, 사인 또는 삼각형)는 OSC_IN 핀을 구동해야 하는 반면, OSC_OUT 핀은 높은 임피던스 상태로 두어야 한다(그림 7 및 그림 6 참조).

3.1.2 외부 수정/세라믹 공진기(HSE 수정)

외부 발진기 주파수 범위는 다음과 같다.

• STM32F101xx, STM32F102xx 및 STM32F103xx 장치에서 4~16MHz

• STM32F100xx 밸류 라인 장치용 4~24MHz

• 연결 회선 장치에서 3 ~ 25MHz

외부 오실레이터는 메인 클록에서 매우 정확한 속도를 생성하는 이점이 있다.

관련 하드웨어 구성은 그림 7에 나와 있다.

공진기와 부하 커패시터는 발진기 핀에 최대한 가깝게 연결해야, 출력 왜곡과 시동 안정화 시간을 최소화할 수 있다. 선택한 발진기에 따라 부하 커패시턴스 값을 조정해야 한다.

CL1 및 CL2의 경우, 5pF ~ 25pF 범위(통상)의 고품질 세라믹 커패시터를 사용하는 것이 좋다. 이 커패시터는 고주파 애플리케이션용으로 설계되었으며, 수정 또는 공진기의 요구 사항을 충족하도록 선택되었다. CL1과 CL2는 일반적으로 동일한 값이다. 크리스털 제조업체는 일반적으로 CL1과 CL2의 직렬 조합인 부하 커패시턴스를 지정한다. PCB 및 MCU 핀 커패시턴스는 CL1 및 CL2의 크기를 조정할 때, 포함되어야 한다(10pF는 결합된 핀 및 보드 커패시턴스의 대략적인 추정치로 사용될 수 있음).

자세한 내용은 데이터시트의 전기적 특성 섹션을 참조하자.

3.2 LSE OSC 클록

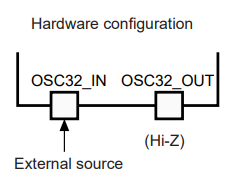

저속 외부 클록 신호(LSE)는 두 가지 가능한 클록 소스에서 생성할 수 있다.

• LSE 외부 수정/세라믹 공진기(그림 9 참조)

• LSE 사용자 외부 클록(그림 8 참조)

그림 8. 외부 클록

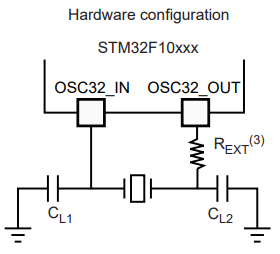

그림 9. 수정/세라믹 공진기

참고:

1 "외부 시계" 그림:

CL1 및 CL2(15pF)의 최대값을 초과하지 않으려면, 부하 커패시턴스 CL ≤ 7pF인 공진기를 사용하는 것이 좋다. 부하 용량이 12.5pF인 공진기는 절대 사용하지 말자.

2 "외부 클록" 및 "크리스털/세라믹 공진기" 수치:

OSC32_IN 및 OSC_OUT 핀은 GPIO로도 사용할 수 있지만 동일한 응용 프로그램에서 RTC 및 GPIO 핀으로 사용하지 않는 것이 좋습니다.

3 "크리스털/세라믹 공진기" 그림:

REXT의 값은 크리스탈 특성에 따라 다르다. 0Ω 저항이 작동하지만 최적은 아니다. 일반적인 값은 5 ~ 6 RS(공진기 직렬 저항) 범위이다. RS 값을 미세 조정하려면, AN2867 - ST 마이크로컨트롤러용 오실레이터 설계 가이드를 참조하자.

3.2.1 외부 소스(LSE 바이패스)

이 모드에서는 외부 클럭 소스가 제공되어야 한다. 최대 1MHz의 주파수를 가질 수 있다. 듀티 사이클이 약 50%인 외부 클록 신호(정사각, 사인 또는 삼각형)는 OSC32_IN 핀을 구동해야 하지만, OSC32_OUT 핀은 하이 임피던스 상태로 두어야 한다(그림 9 및 그림 8 참조).

3.2.2 외부 수정/세라믹 공진기(LSE 수정)

LSE 수정은 32.768kHz 저속 외부 수정 또는 세라믹 공진기이다. 클럭/캘린더 또는 기타 타이밍 기능을 위해, 실시간 클럭 주변 장치(RTC)에 저전력이지만, 매우 정확한 클럭 소스를 제공하는 이점이 있다.

공진기와 부하 커패시터는 발진기 핀에 최대한 가깝게 연결해야 출력 왜곡과 시동 안정화 시간을 최소화할 수 있다. 선택한 발진기에 따라 부하 커패시턴스 값을 조정해야 한다.

3.3 클록 보안 시스템(CSS)

클록 보안 시스템은 소프트웨어로 활성화할 수 있다. 이 경우 HSE 오실레이터 시작 지연 후, 클록 감지기가 활성화되고, 이 오실레이터가 중지되면, 비활성화된다.

• HSE 오실레이터 클록에서 오류가 감지되면, 오실레이터가 자동으로 비활성화된다. 클록 오류 이벤트가 TIM1 고급 제어 타이머의 브레이크 입력으로 전송되고, 인터럽트가 생성되어, 소프트웨어에 오류를 알리므로(클록 보안 시스템 인터럽트 CSSI) MCU가 복구 작업을 수행할 수 있다. CSSI는 Cortex-M3 NMI(마스크 불가능 인터럽트) 예외 벡터에 연결된다.

• HSE 오실레이터를 직접 또는 간접적으로 시스템 클록으로 사용하는 경우(간접적으로는 PLL 입력 클록으로 사용하고 PLL 클록을 시스템 클록으로 사용함을 의미), 오류가 감지되면, 시스템 클록이 HSI 오실레이터로 전환되고, 외부 HSE 오실레이터가 비활성화된다. HSE 오실레이터 클록(분할 여부)이 오류 발생 시, 시스템 클록으로 사용되는 PLL의 클록 항목인 경우, PLL도 비활성화된다.

자세한 내용은 STMicroelectronics 웹 사이트 www.st.com에서 제공되는 STM32F10xxx(RM0008) 및 STM32F100xx(RM0041) 참조 설명서를 참조하자.

4 부팅 구성

4.1 부팅 모드 선택

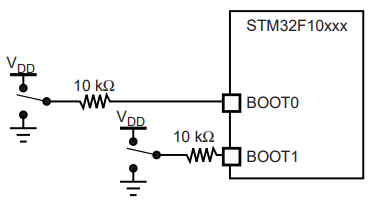

STM32F10xxx에서는 표 2와 같이 BOOT[1:0] 핀을 통해 세 가지 부팅 모드를 선택할 수 있다.

표 2. 부팅 모드

| 부팅 모드 선택 핀 | 부트 모드 | 앨리어싱 | |

| 부트1 | 부트0 | ||

| x | 0 | 메인 플래시 메모리 | 메인 플래시 메모리가 부팅 공간으로 선택됨 |

| 0 | 1 | 시스템 메모리 | 시스템 메모리가 부팅 공간으로 선택됨 |

| 1 | 1 | Embedded SRAM | Embedded SRAM이 부트 공간으로 선택됨 |

BOOT 핀의 값은 재설정 후 SYSCLK의 네 번째 상승 에지에서 래치된다. 필요한 부트 모드를 선택하기 위해, 리셋 후, BOOT1 및 BOOT0 핀을 설정하는 것은 사용자에게 달려 있다.

대기 모드를 종료할 때, BOOT 핀도 리샘플링 된다. 따라서 대기 모드에서 필수 부트 모드 구성을 유지해야 한다. 이 시작 지연이 경과한 후, CPU는 주소 0x0000 0000에서 스택 상단 값을 가져오고, 부트 메모리에서 0x0000 0004부터 시작하여, 코드 실행을 시작한다.

4.2 부트 핀 연결

그림 10은 STM32F10xxx의 부트 메모리를 선택하는 데 필요한 외부 연결을 보여준다.

그림 10. 부팅 모드 선택 구현 예

1. 저항값은 전형적인 예로만 제공된다.

4.3 임베디드 부트로더 모드

임베디드 부트 로더 모드는 사용할 수 있는 직렬 인터페이스 중 하나를 사용하여, 플래시 메모리를 재프로그래밍하는 데 사용된다.

• 저밀도, 저밀도 밸류라인, 중밀도, 중밀도 밸류라인, 고밀도 기기에서 부트로더는 USART1 인터페이스를 통해 활성화된다. 자세한 내용은 AN2606을 참조하자.

• XL 밀도 장치에서 부트 로더는 USART1 또는 USART2(재매핑) 인터페이스를 통해 활성화된다. 자세한 내용은 AN2606을 참조하자.

• 연결 회선 장치에서 부트 로더는 다음 인터페이스 중 하나를 통해 활성화할 수 있다. USART1, USART2(재매핑), CAN2(재매핑) 또는 장치 모드의 USB OTG FS(DFU: 장치 펌웨어 업그레이드). USART 주변 장치는 내부 8MHz 발진기(HSI)와 함께 작동한다. 그러나 CAN 및 USB OTG FS는 외부 8MHz, 14.7456MHz 또는 25MHz 클록(HSE)이 있는 경우에만 작동할 수 있다. 자세한 내용은 AN2662를 참조하자.

이 임베디드 부트 로더는 시스템 메모리에 있으며, 생산 중에 ST에 의해 프로그래밍 된다.

5 디버그 관리

5.1 소개

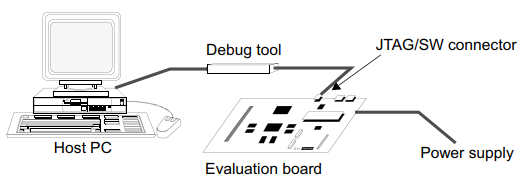

Host/Target 인터페이스는 호스트와 애플리케이션 보드를 연결하는 하드웨어 장비이다. 이 인터페이스는 하드웨어 디버그 도구, JTAG 또는 SW 커넥터 및 디버그 도구에 호스트를 연결하는 케이블의 세 가지 구성 요소로 구성된다.

그림 11은 호스트와 평가 보드(STM3210B-EVAL, STM3210C-EVAL, STM32100B-EVAL 또는 STM3210E-EVAL)의 연결을 보여준다.

밸류 라인 평가 보드(STM32100B-EVAL 또는 STM32100E-EVAL)에는 디버그 도구(ST-LINK)가 내장되어 있다. 따라서 USB 케이블을 통해 PC에 직접 연결할 수 있다.

그림 11. 호스트-보드 연결

5.2 SWJ 디버그 포트(직렬 와이어 및 JTAG)

STM32F10xxx 코어는 직렬 와이어/JTAG 디버그 포트(SWJ-DP)를 통합한다.

JTAG-DP(5핀) 인터페이스와 SW-DP(2핀) 인터페이스를 결합한 Arm® 표준 CoreSight™ 디버그 포트이다.

• JTAG 디버그 포트(JTAG-DP)는 AHPAP 포트에 5핀 표준 JTAG 인터페이스를 제공한다.

• 직렬 와이어 디버그 포트(SW-DP)는 AHP-AP 포트에 2핀(클록 + 데이터) 인터페이스를 제공한다.

SWJ-DP에서 SW-DP의 2개 JTAG 핀은 JTAG-DP의 5개 JTAG 핀 중 일부와 다중화된다.

5.3 핀아웃 및 디버그 포트 핀

STM32F10xxx MCU는 사용할 수 있는 핀 수가 다른 다양한 패키지로 제공된다.

결과적으로 핀 가용성과 관련된 일부 기능은 패키지마다 다를 수 있다.

5.3.1 SWJ 디버그 포트 핀

5개의 핀은 범용 I/O(GPIO)의 대체 기능인 SWJ-DP의 출력으로 사용된다.

표 3에 표시된 이 핀은 모든 패키지에서 사용할 수 있다.

표 3. 디버그 포트 핀 할당

| SWJ-DP 핀 이름 | JTAG 디버그 포트 | SW 디버그 포트 | 핀 할당 | ||

| 유형 | 설명 | 유형 | 디버그 할당 | ||

| JTMS/SWDIO | I | JTAG 테스트 모드 선택 | I/O | 직렬 와이어 데이터 입력/출력 | PA13 |

| JTCK/SWCLK | I | JTAG 테스트 클록 | I | 직렬 와이어 클록 | PA14 |

| JTDI | I | JTAG 테스트 데이터 입력 | - | - | PA15 |

| JTDO/TRACESWO | O | JTAG 테스트 데이터 출력 | - | 비동기 추적인 경우 TRACESWO 활성화됨 |

PB3 |

| JNTRST | I | JTAG 테스트 nReset | - | - | PB4 |

5.3.2 유연한 SWJ-DP 핀 할당

리셋(SYSRESETn 또는 PORESETn) 후, SWJ-DP에 사용되는 5개의 핀 모두 디버거 호스트에서 즉시 사용할 수 있는 전용 핀으로 할당된다(디버거 호스트에서 명시적으로 프로그래밍된 경우를 제외하고, 추적 출력은 할당되지 않음).

그러나 STM32F10xxx MCU는 레지스터를 구현하여, SWJ-DP 포트의 일부 또는 전체를 비활성화하므로 범용 I/O 사용을 위해 관련 핀을 해제한다. 이 레지스터는 Cortex-M3 시스템 버스에 연결된 APB 브리지에 매핑된다. 이 레지스터는 디버거 호스트가 아닌 사용자 소프트웨어 프로그램으로 프로그래밍 된다.

표 4. SWJ I/O 핀 가용성

| 사용 가능한 디버그 포트 | SWJ I/O 핀 할당 | ||||

| PA13 / JTMS/ SWDIO |

PA14 / JTCK/ SWCLK |

PA15 / JTDI |

PB3 / JTDO |

PB4/ JNTRST |

|

| 전체 SWJ(JTAG-DP + SW-DP) - 재설정 상태 | X | X | X | X | X |

| 전체 SWJ(JTAG-DP + SW-DP), JNTRST 없음 | X | X | X | X | |

| JTAG-DP 비활성화 및 SW-DP 활성화 | X | X | |||

| JTAG-DP 비활성화 및 SW-DP 비활성화 출시 | |||||

표 4는 일부 핀을 해제할 수 있는 다양한 가능성을 보여준다.

자세한 내용은 STMicroelectronics 웹 사이트 www.st.com에서 제공되는 STM32F10xxx(RM0008) 및 STM32F100xx(RM0041) 참조 설명서를 참조하자.

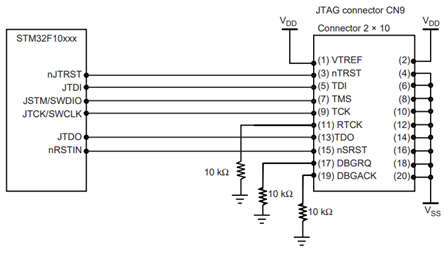

5.3.3 JTAG 핀의 내부 풀업 및 풀다운 저항

JTAG 입력 핀은 디버그 모드 기능을 제어하기 위해 플립플롭에 직접 연결되어 있어서, 부동 상태가 아니어야 한다. 이러한 플립플롭 중 일부의 클록에 직접 연결된 SWCLK/TCK 핀에 특별한 주의를 기울여야 한다.

제어되지 않는 I/O 레벨을 피하기 위해, STM32F10xxx는 JTAG 입력 핀에 내부 풀업 및 풀다운 저항을 내장한다.

• JNTRST: 내부 풀업

• JTDI: 내부 풀업

• JTMS/SWDIO: 내부 풀업

• TCK/SWCLK: 내부 풀다운

사용자 소프트웨어에 의해, JTAG I/O가 해제되면, GPIO 컨트롤러가 다시 제어한다.

GPIO 제어 레지스터의 리셋 상태는 I/O를 같은 상태로 만든다.

• JNTRST: 입력 풀업

• JTDI: 입력 풀업

• JTMS/SWDIO: 입력 풀업

• JTCK/SWCLK: 입력 풀다운

• JTDO: 입력 부동

그런 다음 소프트웨어는 이러한 I/O를 표준 GPIO로 사용할 수 있다.

참고: JTAG IEEE 표준은 TDI, TMS 및 nTRST에 풀업 저항을 추가할 것을 권장하지만 TCK에 대한 특별한 권장 사항은 없다. 그러나 STM32F10xxx의 경우, 통합 풀다운 저항이 JTCK에 사용된다. 풀업 및 풀다운 저항이 내장되어 있어서, 외부 저항이 필요하지 않다.

5.3.4 표준 JTAG 커넥터와 SWJ 디버그 포트 연결

그림 12는 STM32F10xxx와 표준 JTAG 커넥터 간의 연결을 보여준다.

그림 12. JTAG 커넥터 구현

6 추천

6.1 인쇄 회로 기판

기술적인 이유로 별도의 접지 전용 레이어(VSS)와 VDD 공급 전용 레이어가 있는 다층 인쇄 회로 기판(PCB)을 사용하는 것이 가장 좋다. 이는 우수한 디커플링 및 우수한 차폐 효과를 제공한다. 많은 애플리케이션에서 경제적인 이유로 이러한 유형의 보드를 사용하지 않게 된다. 이 경우 주요 요구 사항은 접지 및 전원 공급 장치에 대한 좋은 구조를 확보하는 것이다.

6.2 구성 요소 위치

PCB의 예비 레이아웃은 잡음이 많은 고전류 회로, 저전압 회로 및 디지털 부품인 PCB의 교차 결합을 줄이기 위해, EMI 기여도에 따라 서로 다른 회로를 분리해야 한다.

6.3 접지 및 전원 공급(VSS, VDD)

모든 블록(노이즈, 저레벨 민감, 디지털 등)은 개별적으로 접지되어야 하며, 모든 접지 복귀는 단일 지점으로 이루어져야 한다. 루프는 피하거나 최소한의 면적을 가져야 한다. 전원 공급 장치는 공급 루프의 영역을 최소화하기 위해서 접지선 가까이에 구현되어야 한다. 이는 공급 루프가 안테나 역할을 하므로, EMI의 주요한 송신기와 수신기가 될 수 있기 때문이다. 부품이 없는 모든 PCB 영역은 일종의 차폐를 만들기 위해서, 추가 접지로 채워야 한다(특히 단일 레이어 PCB를 사용하는 경우).

6.4 디커플링

모든 전원 공급 장치와 접지 핀은 전원 공급 장치에 올바르게 연결되어야 한다. 패드, 트랙 및 비아를 포함한 이러한 연결은 가능한 한, 낮은 임피던스를 가져야 한다. 이는 일반적으로 두꺼운 트랙 폭과 바람직하게는 다층 PCB에서 전용 전원 공급 장치를 사용하여 달성하게 된다.

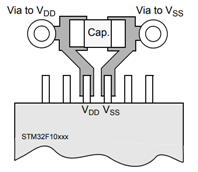

더불어, 각 전원 공급 장치 쌍은 필터링 세라믹 커패시터 C(100nF)와 STM32F10xxx 장치에서 병렬로 연결된 약 10µF의 전해 커패시터 C와 분리되어야 한다. 이러한 커패시터는 PCB 밑면에 있는 적절한 핀에 가능한 한 가깝도록, 또는 부품의 바로 아래에 배치해야 한다. 일반적인 값은 10nF ~ 100nF이지만, 정확한 값은 애플리케이션 요구 사항에 따라 다르다. 그림 13은 이러한 VDD/VSS 쌍의 일반적인 레이아웃을 보여준다.

그림 13. VDD/VSS 쌍의 일반적인 레이아웃

6.5 기타 신호들

애플리케이션을 설계할 때, 다음을 자세히 연구하여, EMC 성능을 향상할 수 있다.

• 일시적 방해가 실행 중인 프로세스에 영구적으로 영향을 미치는 신호(인터럽트 및 핸드-쉐이킹 스트로브 신호의 경우이며, LED 명령의 경우는 아님). 이러한 신호의 경우, 주변 접지 트레이스, 더 짧은 길이, 주변에 잡음이 많고 민감한 트레이스(누화 효과)가 없어서, EMC 성능이 향상된다. 디지털 신호의 경우에는 두 논리 상태에 대해서 가능한 최상의 전기 마진에 도달해야 하며, 기생 상태를 제거하기 위해, 느린 슈미트 트리거가 권장된다.

• 노이즈 신호(예: 클록)

• 민감한 신호(임피던스가 높은 신호 등)

6.6 미사용 I/O 및 기능

모든 마이크로컨트롤러는 다양한 애플리케이션용으로 설계되었으며, 특정 애플리케이션이 MCU 리소스를 100% 사용하지 않는 경우가 많다.

EMC 성능을 높이려면, 사용하지 않는 클록, 카운터 또는 I/O를 비워두어서는 안 된다.

I/O는 "0" 또는 "1"(사용하지 않는 I/O 핀에 대한 풀업 또는 풀다운)으로 설정해야 하며 사용하지 않는 기능은 "고정" 또는 비활성화해야 한다.

7 참조 디자인

7.1 설명

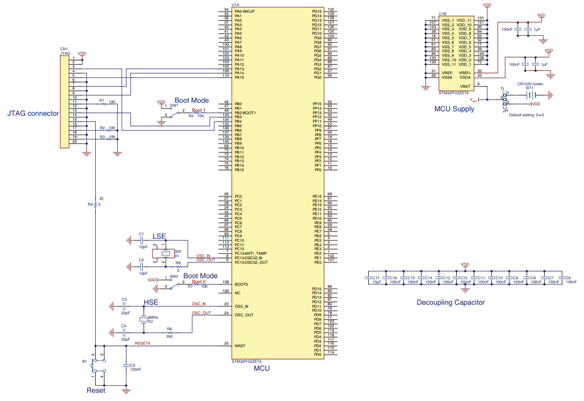

그림 14에 표시된 참조 설계는 72MHz에서 실행되는 고집적 마이크로컨트롤러인 STM32F103ZE(T6)를 기반으로 하며, 새로운 Cortex™-M3 32비트 RISC CPU 코어를 512KB의 내장형 플래시 메모리 및 최대 64KB의 고속 SRAM과 결합한다.

이 기준 설계는 표 7에 제공된 핀 대응을 사용하여, 패키지가 다른 STM32F10xxx 장치에 맞출 수 있다.

7.1.1 클록

마이크로컨트롤러에는 두 개의 클록 소스가 사용된다.

• LSE: 임베디드 RTC용 X1– 32.768kHz 크리스털

• HSE: STM32F10xxx 마이크로컨트롤러용 X2– 8MHz 크리스털

섹션 3을 참조하자.

7.1.2 리셋

그림 14의 리셋 신호는 액티브 Low이다. 리셋 소스에는 다음이 포함된다.

• 리셋 버튼(B1)

• 커넥터 CN1을 통한 디버깅 도구

섹션 2.3을 참조하자.

7.1.3 부팅 모드

부팅 옵션은 스위치 SW2(부팅 0) 및 SW1(부팅 1)을 설정하여 구성된다.

섹션 4를 참조하자.

참고:

저전력 모드(특히 대기 모드)에서 도구에 연결하려면, 부팅 모드가 필수이다(SRAM에서 장치 부팅).

7.1.4 SWJ 인터페이스

참조 설계는 STM32F10xxx와 표준 JTAG 커넥터 간의 연결을 보여준다. 섹션 5를 참조하자.

참고:

도구에서 애플리케이션을 재설정할 수 있도록 재설정 핀을 연결하는 것이 좋습니다.

7.1.5 전원 공급

섹션 2를 참조하자.

7.2 컴포넌트 참조

표 5. 필수 구성 요소

| ID | 이름 | 참조 | 수량 | 설명 |

| 1 | 마이크로컨트롤러 | STM32F103ZE(T6) | 1 | 144핀 패키지 |

| 2 | 커패시터 | 100nF | 11 | 세라믹 커패시터(디커플링 커패시터) |

| 3 | 커패시터 | 10µF | 1 | 세라믹 커패시터(디커플링 커패시터) |

표 6. 선택적 구성 요소

| ID | 이름 | 참조 | 수량 | 설명 |

| 1 | 저항 | 10kΩ | 5 | JTAG 및 부트 모드용 풀업 및 풀다운 |

| 2 | 저항기 | 390Ω | 1 | HSE에 사용: 값은 크리스탈 특성에 따라 다르다. 이 저항값은 일반적인 예로만 제공된다. |

| 3 | 저항기 | 0Ω | 1 | LSE에 사용: 결정 특성에 따라 값이 달라진다. 이 저항값은 일반적인 예로만 제공된다. |

| 4 | 커패시터 | 100nF | 3 | 세라믹 커패시터 |

| 5 | 커패시터 | 1µF | 2 | VDDA 및 VREF에 사용된다. |

| 6 | 커패시터 | 10pF | 2 | LSE에 사용: 값은 크리스탈 특성에 따라 다름 |

| 7 | 커패시터 | 20pF | 2 | HSE에 사용됨: 값은 크리스탈 특성에 따라 다름 |

| 8 | 크리스탈 쿼츠 | 8MHz | 1 | HSE에 사용됨 |

| 9 | 크리스탈 쿼츠 | 32kHz | 1 | LSE에 사용 |

| 10 | JTAG 커넥터 | HE10 | 1 | - |

| 11 | 배터리 | 3V3 | 1 | 애플리케이션에서 외부 배터리를 사용하지 않으면, VBAT를 VDD에 외부적으로 연결하는 것이 좋다. |

| 12 | 스위치 | 3V3 | 2 | 올바른 부팅 모드를 선택하는 데 사용 |

| 13 | 푸시 버튼 | B1 | 1 | - |

그림 14. STM32F103ZE(T6) 마이크로컨트롤러 참조 회로도

1. 애플리케이션에서 외부 배터리를 사용하지 않는 경우 VBAT를 외부에서 VDD에 연결하는 것이 좋다.

2. 도구에서 장치를 재설정하려면 이 저항기를 보관해야 한다.

표 7. 모든 패키지에 대한 참조 연결

| 핀 이름 | LQFP 패키지용 핀 번호 | BGA 패키지 핀 번호 |

VFQFPN 패키지 핀 번호 |

||||

| 144핀 | 100핀 | 64핀 | 48핀 | 144핀 | 100핀 | 36핀 | |

| OSC_IN | 23 | 12 | 5 | 5 | D1 | C1 | 2 |

| OSC_OUT | 24 | 13 | 6 | 6 | E1 | D1 | 3 |

| PC15-OSC32_OUT | 9 | 9 | 4 | 4 | C1 | B1 | - |

| PC14-OSC32_IN | 8 | 8 | 3 | 3 | B1 | A1 | - |

| BOOT0 | 138 | 94 | 28 | 20 | D5 | D5 | 35 |

| PB2-BOOT1 | 48 | 37 | 28 | 20 | J5 | G5 | 17 |

| NRST | 25 | 14 | 7 | 7 | F1 | E1 | 4 |

| PA13 | 105 | 72 | 46 | 34 | A12 | A10 | 25 |

| PA14 | 109 | 76 | 49 | 37 | A11 | A9 | 28 |

| PA15 | 110 | 77 | 50 | 38 | A10 | A8 | 29 |

| PB4 | 134 | 90 | 56 | 40 | A6 | A6 | 31 |

| PB3 | 133 | 89 | 55 | 39 | A7 | A7 | 30 |

| VSS_1 | 71 | 49 | 31 | 23 | H7 | E7 | 18 |

| VSS_2 | 107 | 74 | 47 | 35 | G9 | E6 | 26 |

| VSS_3 | 143 | 99 | 63 | 47 | E5 | E5 | 36 |

| VSS_4 | 38 | 27 | 18 | - | G4 | E4 | - |

| VSS_5 | 16 | 10 | - | - | D2 | C2 | - |

| VSS_6 | 51 | - | - | - | H5 | - | - |

| VSS_7 | 61 | - | - | - | H6 | - | - |

| VSS_8 | 83 | - | - | - | G8 | - | - |

| VSS_9 | 94 | - | - | - | G10 | - | - |

| VSS_10 | 120 | - | - | - | E7 | - | - |

| VSS_11 | 130 | - | - | - | E6 | - | - |

| VDD_1 | 72 | 50 | 32 | 24 | G7 | F7 | 19 |

| VDD_2 | 108 | 75 | 48 | 36 | F9 | 27 | |

| VDD_3 | 144 | 100 | 64 | 48 | F5 | F5 | 1 |

| VDD_4 | 39 | 28 | 19 | - | F4 | F4 | - |

| VDD_5 | 17 | 11 | - | - | D3 | D2 | - |

| VDD_6 | 52 | - | - | - | G5 | - | - |

| VDD_7 | 62 | - | - | - | G6 | - | - |

| VDD_8 | 84 | - | - | - | F8 | - | - |

| VDD_9 | 95 | - | - | - | F10 | - | - |

| VDD_10 | 121 | - | - | - | F7 | - | - |

| VDD_11 | 131 | - | - | - | F6 | - | - |

| VREF+ | 32 | 21 | - | - | L1 | J1 | - |

| VREF- | 31 | 20 | - | - | K1 | H1 | - |

| VSSA | 30 | 19 | 12 | 8 | J1 | G1 | - |

| VDDA | 33 | 22 | 13 | 9 | M1 | K1 | - |

| VBAT | 6 | 6 | 1 | 1 | C2 | B2 | - |

8. 개정 이력

== 생략 ==

'STM32 MCU' 카테고리의 다른 글

| ARM Cortex-M3 STM32F103 MCU (0) | 2023.04.22 |

|---|---|

| STM32 MCU의 명명 규칙 이해 (0) | 2023.03.05 |

| STM32 MCU 들어다 보기 (0) | 2023.03.04 |